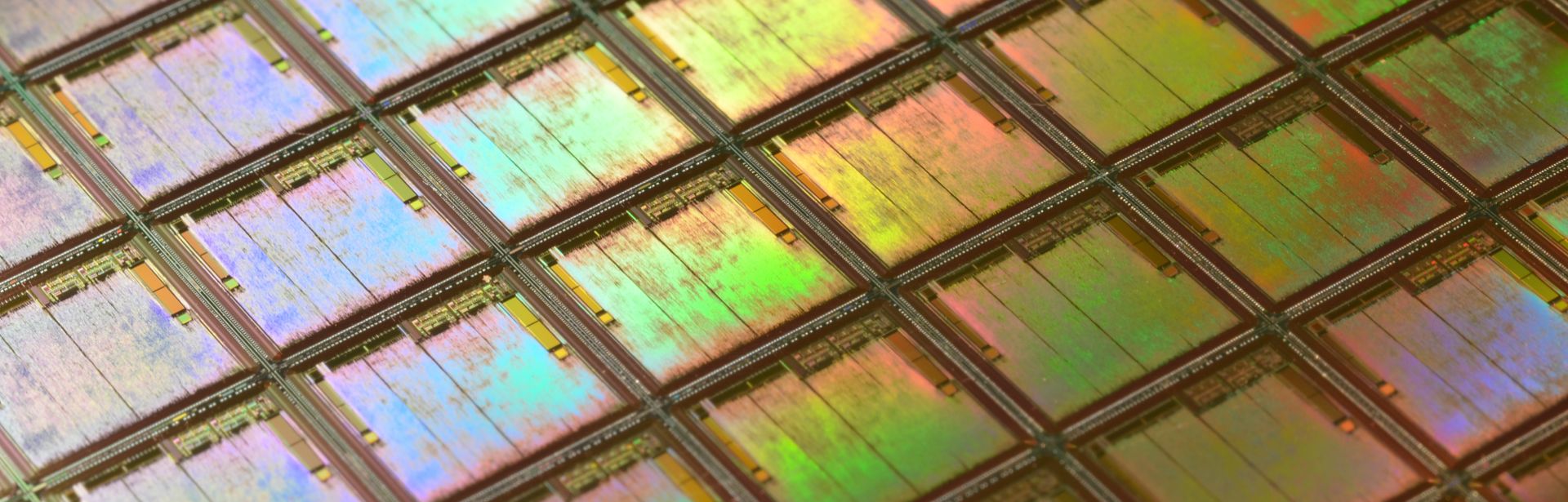

Chiplet降低先進製程設計難度,讓摩爾定律有望延續

2023.11/02

|

產業趨勢探勘

- 隨著晶片製程的持續演進,發熱、漏電等問題愈發嚴重,加上先進製程下高昂的晶片研發、製造費用也給IC設計公司帶來巨大的成本壓力與投資風險,導致摩爾定律日趨放緩。

- 為了開發功能更複雜的晶片,IC設計商需要設計一種將所有功能放在同一晶片上,變成系統單晶片產品(System on Chip)。尤其在最新的7nm、5nm、3nm製程上,成本和複雜性飆升。

- 在摩爾定律推進速度放慢與先進製程成本增加的情況下,IC設計業者開始採用Chiplet(小晶片)架構,透過先進封裝技術的整合,不僅在成本方面具有競爭力,而且可以提升元件效能,或實現更複雜的功能。

- Chiplet就是將原本一塊SoC晶片,依照不同的計算單元或功能單元選擇最適合的製程進行製造,再透過先進封裝技術連接不同製程的模組化晶片,封裝成一個SoC晶片而使之成為異質整合晶片。例如仰賴先進製程的運算單元如CPU和GPU,可以採用先進製程生產,而不受製程工藝影響的功能單元如IO部分,則可以採用成本較低的成熟製程製造,以此來降低成本和提升良率。使其超越單純只靠先進製程晶片的性能、效率,同時實現低成本和高良率,因此Chiplet有機會成為超越摩爾定律物理極限的關鍵技術。

- 透過Chiplet技術,能在系統單晶片製程在轉移時,降低每一次製程縮減所需要的成本和開發時間。僅在最新製程中引入必要的運算單元,再藉由先進封裝進行連接。因此Chiplet在架構設計、後端和封裝流程的重要性比前端設計更為重要。

- 在生成式AI的推波助瀾之下,雲端AI服務於今年出現爆炸性成長,同時也帶動邊緣AI的發展,然而由於成本及效能考量,邊緣AI的運算更仰賴Chiplet技術,於擁有極高的算力之下仍保持極高的良率。

- 據Omdia報告,預計到2024年,Chiplet市場規模將達到58億美元,2035年將超過570億美元,市場規模將迎來快速增長。

- Chiplet除了具備匯流排的互聯技術外,還需要靠封裝技術達到晶片的異質整合,因此晶片從設計端就必須要考量到後段整合的問題,儘管可以降低先進製程設計難度,但對於封裝設計也是一大挑戰。

Chiplet連接標準百花齊放,UCIe成為首選標準

- 然而Chiplet因不同製造商生產的晶片之間的互連接口和協議的不同,必須考慮到製程、封裝技術、系統整合、擴展等諸多複雜因素。同時還要滿足不同領域、不同場景對訊號傳輸速度、功耗等方面的要求,使得Chiplet在整合上異常困難。

- 各晶片巨頭都在推自己的互聯標準,例如Marvell採用Kandou匯流排介面;Nvidia用於GPU的高速互聯NV Link方案;Intel免費向外界授權的AIB先進介面匯流排;台積電和Arm合作推出的LIPINCON協議;AMD也有Infinity Fabric技術,以及用於儲存晶片堆疊的HBM接口等。又如蘋果發布的M1 Ultra晶片,通過Chiplet封裝方案將兩個M1 Max晶片互連,以實現更高的性能以及更經濟的方案。

- Intel於2022年提出的通用Chiplet互聯標準Universal Chiplet Interconnect Express (UCIe),希望在晶片封裝層面確立連接的統一標準,以幫助在整個半導體行業建立一個開放的小晶片生態系統。

- UCIe標準的推出對半導體行業帶來巨大的影響,讓各家晶片巨頭們合力搭建起了統一的Chiplet連接標準,讓終端使用者在打造SoC晶片時,可以自由搭配來自多個廠商生態系統中的晶片功能模組,並橫跨x86、Arm、RISC-V等架構和指令集,這將加速Chiplet平台發展。

- UCIe聯盟由Intel推動,於 2022年3月成立,目前聯盟成員已達120家以上。互聯標準也已更新至UCIe 1.1版本,已涵蓋2D、2.5D(EMIB、CoWoS、FOCoS)封裝架構標準,3D封裝則尚未推出。

- 目前Intel Sapphire Rapids和最新發布的Meteor Lake處理器都採用了Chiplet設計,但仍使用Intel專有先進介面匯流排(AIB);但 後續Arrow Lake處理器之後將開始採用UCIe介面,未來台廠率先投入之公司將可望受惠。

- 由於小晶片先進封裝涉及不同次產業,生態系統龐大,台廠挾上下游供應鏈完整之優勢,率先卡位次世代技術,無論是源頭IP、IC設計乃至下游晶圓製造,預期在不久的未來,不同製程、IP的晶片融合在同一個封裝內,將會變得司空見慣。

Chiplet相關台廠及其發展中的技術摘要

|

次領域 |

企業 |

發展近況 |

|

矽智財 |

創意 |

|

|

世芯 |

|

|

|

智原 |

|

|

|

愛普 |

|

|

|

記憶體 |

華邦電 |

|

|

鈺創 |

|

|

|

封裝 |

日月光 |

|

|

力成 |

|

GoldON投資方向思考

- 台灣具備完整的半導體生態系,從先進製程代工、矽智財服務到封裝測試都能夠快速整合,由於Chiplet技術需要上下游能夠縝密的整合,而台灣廠商利用自己的封裝設計及製造技術來協助各家巨頭完成Chiplet,不論是矽智財廠、記憶體廠以及封測廠都切入到關鍵技術,因此台灣極具發展Chiplet的潛力。

- 儘管Intel發起了UCIe聯盟希望可以統一標準,然而各家貢獻者仍處於工程樣品開發的階段,包括發起人Intel本身也於今年9月才完成第一個樣品,因此預計UCIe真正商業化的時間可能會等到2025年。

- 然而,2024年預計是邊緣AI大幅成長的一年,預計推出的AI PC/NB和AI手機將帶動久違的換機潮,同時也將是Chiplet市場爆發展開的一年,屆時從台積電的CoWoS製造、矽智財、封裝設計甚至到封裝廠的封裝服務,預料都將會有不小的成長動能。

關於本篇

前驅投資週報_2023-027

Processor: Shawn Hung

Hunter: Shawn Hung